SPI接口DAC驱动CBB设计

SPI接口DAC驱动CBB设计

渔火版本信息

- 版本号:1.0

- 编写时间:2024.03.12

变更日志

- 2024.03.12:初稿

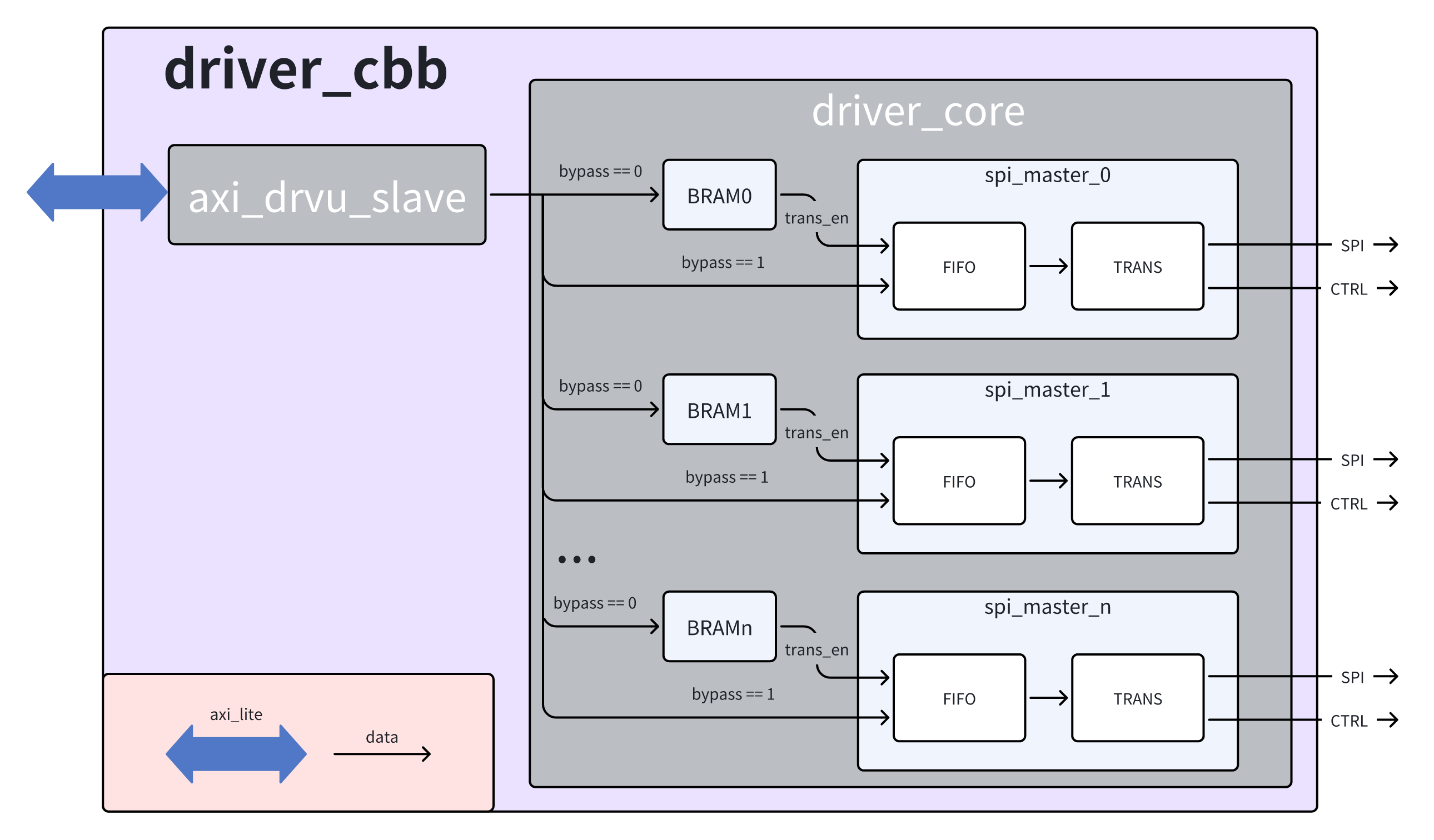

系统框图

driver_cbb的系统框图如图所示。系统内部由axi_drvu_slave模块和driver_core两个模块组成,其中axi_drvu_slave模块用于与CPU通讯,CPU将控制信号与数据信号通过axi-lite接口传输给axi_drvu_slave模块。数据信号根据控制信号,选择是否存入driver_core模块里的BRAM中。若不存入,数据直接流向spi_master模块中,经过FIFO缓存后,直接输出SPI信号。若存入,则在存入之前需要设置存入数据的大小(该大小同时对所有通道生效)。BRAM数据写入完成后,控制信号控制系统从BRAM中读取数据传输给spi_master模块并输出SPI信号。

用户接口

用户参数

| Name | Description |

|---|---|

| DAC_NUM | DAC芯片个数,大小不超过128 |

| DAC_GROUP | DAC芯片组数,必须能被DAC芯片个数整除,每一组DAC芯片共用同一个sck、cs和update信号 |

| MEMORY_ADDR | BRAM存储地址位宽,BRAM存储大小:2^MEMORY_ADDR,MEMORY_ADDR不大于16 |

| FIFO_DEPTH | FIFO深度,大小必须为2的n次幂,n为正整数 |

| SPI_LINE | SPI信号类型,1:SPI 2:DSPI 4:QSPI |

信号接口

| Name | Bit Width | IO Type | Description |

|---|---|---|---|

| clk | 1 | input | driver_cbb工作时钟 |

| rstn | 1 | input | driver_cbb复位信号,低有效 |

| axi_drvu_awaddr | 32 | input | axi-lite接口写地址信号 |

| axi_drvu_awprot | 3 | input | axi-lite接口写地址事务保护类型信号 |

| axi_drvu_awvalid | 1 | input | axi-lite接口写地址有效信号 |

| axi_drvu_awready | 1 | output | axi-lite接口写地址ready信号 |

| axi_drvu_wdata | 32 | input | axi-lite接口写数据信号 |

| axi_drvu_wstrb | 4 | input | axi-lite接口写数据选通信号 |

| axi_drvu_wvalid | 1 | input | axi-lite接口写数据有效信号 |

| axi_drvu_wready | 1 | output | axi-lite接口写数据ready信号 |

| axi_drvu_bready | 1 | input | axi-lite接口写响应ready信号 |

| axi_drvu_bresp | 2 | output | axi-lite接口写事务状态 |

| axi_drvu_bvalid | 1 | output | axi-lite接口写事务有效信号 |

| axi_drvu_araddr | 32 | input | axi-lite接口读地址信号 |

| axi_drvu_arprot | 3 | input | axi-lite接口读地址事务保护类型信号 |

| axi_drvu_arvalid | 1 | input | axi-lite接口读地址有效信号 |

| axi_drvu_arready | 1 | output | axi-lite接口读地址ready信号 |

| axi_drvu_rready | 1 | input | axi-lite接口读数据ready信号 |

| axi_drvu_rdata | 32 | output | axi-lite接口读数据信号 |

| axi_drvu_rresp | 2 | output | axi-lite接口读响应状态信号 |

| axi_drvu_rvalid | 1 | output | axi-lite接口读数据有效信号 |

| sdio0 | DAC_NUM | inout | SPI数据信号0 |

| sdio1 | DAC_NUM | inout | SPI数据信号1(SPI_LINE==1时无效) |

| sdio2 | DAC_NUM | inout | SPI数据信号2(SPI_LINE==1,2时无效) |

| sdio3 | DAC_NUM | inout | SPI数据信号3(SPI_LINE==1,2时无效) |

| sck | DAC_GROUP | output | SPI时钟信号 |

| cs | DAC_GROUP | output | SPI片选信号 |

| up | DAC_GROUP | output | DAC芯片update信号 |

| dir | DAC_NUM | output | 双向电平转换芯片方向控制信号 |

寄存器列表

| Addr[15:0] | RegName[31:0] | CtrlOut | FieldName | Type | LSB | MSB | Description |

|---|---|---|---|---|---|---|---|

| 0 | CHOOSE0 | NO | choose0 | RW | 0 | 31 | 同步模式,选择输出的DAC芯片(0~31) |

| 4 | CHOOSE1 | NO | choose1 | RW | 0 | 31 | 同步模式,选择输出的DAC芯片(32~63) |

| 8 | CHOOSE2 | NO | choose2 | RW | 0 | 31 | 同步模式,选择输出的DAC芯片(64~95) |

| C | CHOOSE3 | NO | choose3 | RW | 0 | 31 | 同步模式,选择输出的DAC芯片(96~127) |

| 10 | SPI_GENERAL | NO | cpol | RW | 0 | 0 | SPI信号极性 |

| cpha | RW | 1 | 1 | SPI信号相位 | |||

| wpol | RW | 2 | 2 | SPI指令读写位极性 | |||

| stream | RW | 3 | 3 | SPI的流模式开关,1开启,0关闭 | |||

| ddr | RW | 4 | 4 | SPI的DDR模式开关,1开启,0关闭 | |||

| clk_div | RW | 5 | 10 | SPI的时钟分频 | |||

| addr_wd | RW | 11 | 16 | SPI指令地址位宽 | |||

| data_wd | RW | 17 | 22 | SPI指令数据位宽 | |||

| 14 | SPI_CS | NO | cs_fall | RW | 0 | 7 | cs信号下降沿延迟,单位为未分频时钟周期 |

| cs_rise | RW | 8 | 15 | cs信号上升沿延迟,单位为未分频时钟周期 | |||

| cs_len | RW | 16 | 23 | 指令之间cs信号长度,单位为未分频时钟周期 | |||

| 18 | UPDATE | NO | up_dly | RW | 0 | 7 | updata信号延迟,单位为未分频时钟周期 |

| up_len | RW | 8 | 15 | updata信号长度,单位为未分频时钟周期 | |||

| up_pol | RW | 16 | 16 | updata信号极性 | |||

| dir_pol | RW | 17 | 17 | 控制外部电平转换芯片的电平极性 | |||

| 1C | DATA_SAVE | NO | data_szie | RW | 0 | 15 | 存储到BRAM中的数据量大小 |

| loop | RW | 16 | 16 | 读取BRAM数据时是否循环 | |||

| pass_by | RW | 17 | 17 | 是否启用BRAM存储数据 | |||

| 20 | TRANS_CTRL | NO | start | RW | 0 | 0 | 开始读出BRAM数据 |

| stop | RW | 1 | 1 | 停止读出BRAM数据 | |||

| 30~30+4n | DATA(n) | NO | tx_dat(n) | RW | 0 | 31 | 准备通过SPI输出的数据,n为DAC芯片序号 |

控制流程

该系统有两种输出模式,异步输出和同步输出。

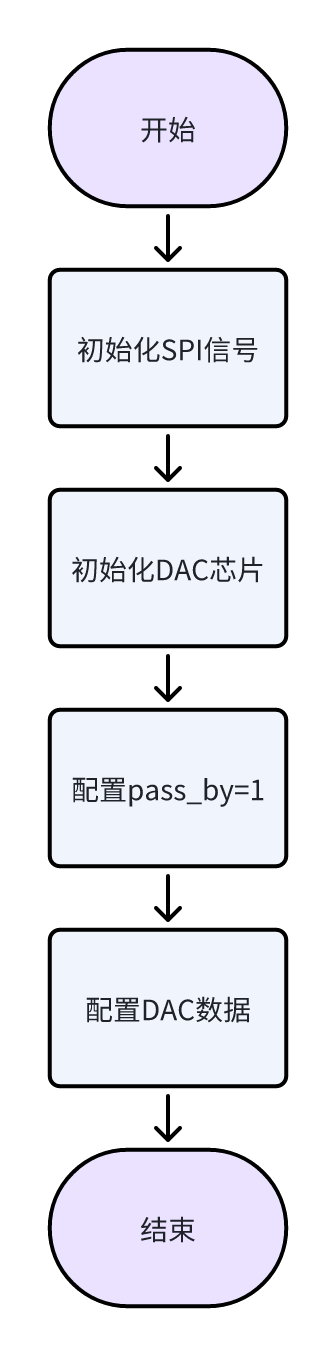

异步模式

异步输出模式下,数据不经过BRAM存储,CPU发送的所有数据经过FIFO缓存后,直接通过SPI信号输出到DAC中,因此该模式下需要注意一次发送的数据量不能超过FIFO的缓存大小(1024),否则则会出现数据丢失的现象。由于每次只能发送一个32bit的数据,因此无法使用SPI的流模式。该模式下的控制流程如下:

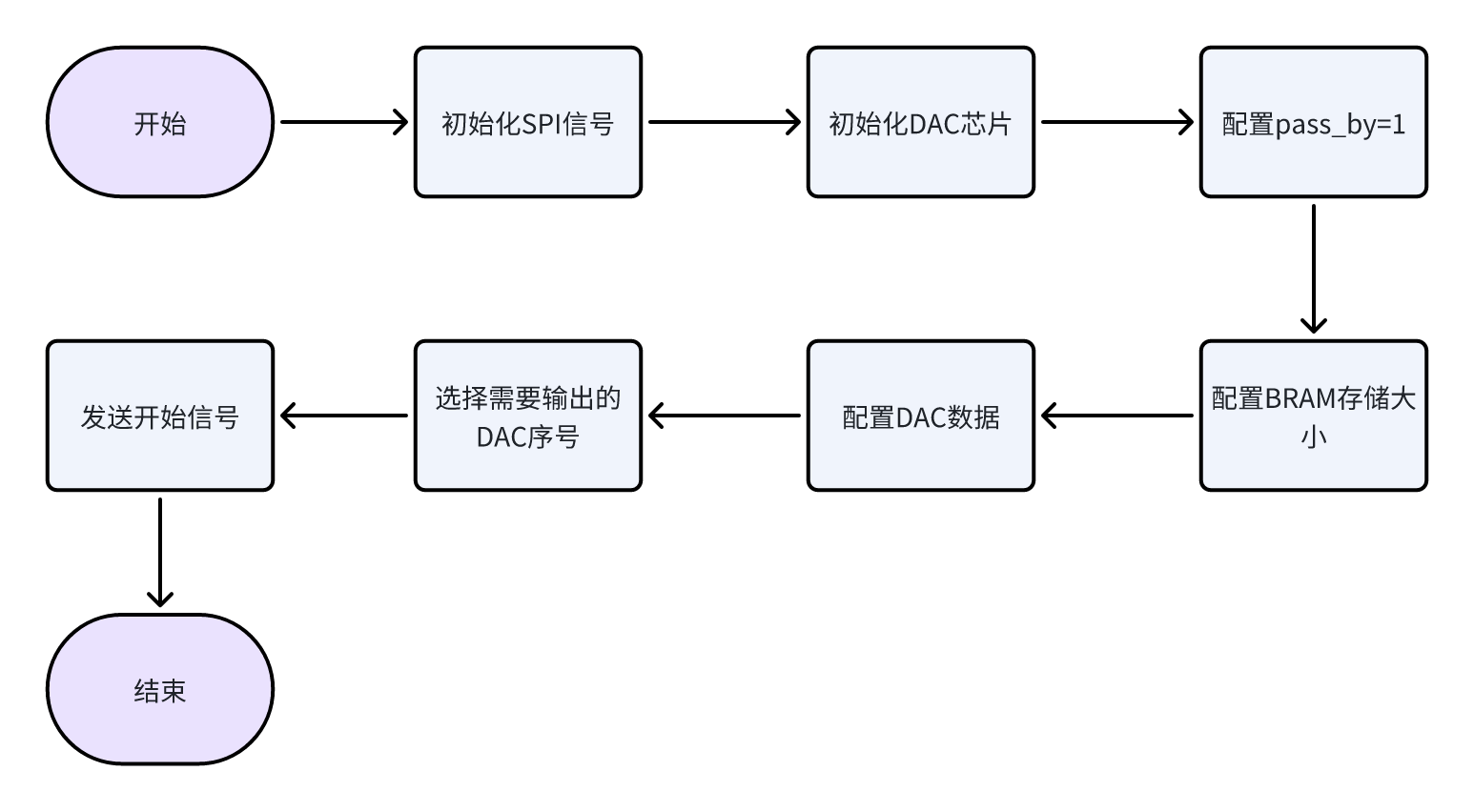

同步模式

同步模式下,CPU先将数据写入BRAM中,等需要输出的DAC所对应的BRAM全部写完成后,发送start信号同时将选中的DAC数据从BRAM读出并通过SPI发送给DAC芯片。该模式下的控制流程如下所示。

评论

匿名评论隐私政策

✅ 你无需删除空行,直接评论以获取最佳展示效果